DEZ J-11 - DEC J-11

Der J-11 ist ein Mikroprozessor- Chipsatz, der die gemeinsam von Digital Equipment Corporation und Harris Semiconductor entwickelte PDP-11- Befehlssatzarchitektur (ISA) implementiert . Es war ein High-End-Chipsatz, der die Leistung und Funktionen des PDP-11/70 auf eine Handvoll Chips integrieren sollte. Es wurde im PDP-11/73 , PDP-11/83 und Professional 380 verwendet .

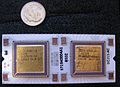

Es bestand aus einem Datenpfadchip und einem Steuerchip in bleifreien Keramikgehäusen, die auf einem einzelnen Keramikhybrid-DIP-Gehäuse montiert waren. Der Steuerchip enthielt einen Steuersequenzer und ein Mikrocode-ROM. Ein optionaler separater FPA-Chip (Floating Point Accelerator) konnte verwendet werden und war in einem Standard-DIP verpackt. Der Datenpfadchip und der Steuerchip wurden von Harris in einem CMOS-Prozess hergestellt, während der FPA von Digital in ihrem " ZMOS " -NMOS- Prozess hergestellt wurde.

Das Design sollte ursprünglich mehrere Steuerchips unterstützen, um die Implementierung zusätzlicher Anweisungen wie des Commercial Instruction Set (CIS) zu ermöglichen. Es wurden jedoch nie solche Steuerchips angeboten.

Ein Klon des J-11 wurde in der Sowjetunion unter der Bezeichnung KN1831VM1 ( russisch : 311831ВМ1 ) hergestellt.