IBM 7030 Stretch - IBM 7030 Stretch

| IBM Stretch | |

|---|---|

IBM 7030 Wartungskonsole im Musée des Arts et Métiers , Paris

| |

| Entwurf | |

| Hersteller | IBM |

| Designer | Gene Amdahl |

| Veröffentlichungsdatum | Mai 1961 |

| Einheiten verkauft | 9 |

| Preis | 7.780.000 US-Dollar (entspricht 67.380.000 US-Dollar im Jahr 2020) |

| Gehäuse | |

| Gewicht | 70.000 Pfund (35 Short Tons; 32 t) |

| Leistung | 100 kW bei 110 V |

| System | |

| Betriebssystem | MCP |

| Zentralprozessor | 64-Bit- Prozessor |

| Speicher | 2048 Kilobyte (262144 x 64 Bit) |

| MIPS | 1,2 MIPS |

Der IBM 7030 , auch bekannt als Stretch , war der erste Transistor- Supercomputer von IBM . Er war von 1961 bis zur Inbetriebnahme des ersten CDC 6600 im Jahr 1964 der schnellste Computer der Welt .

Ursprünglich entworfen, um eine von Edward Teller am Lawrence Livermore National Laboratory formulierte Anforderung zu erfüllen , wurde das erste Exemplar 1961 an das Los Alamos National Laboratory und eine zweite angepasste Version, die IBM 7950 Harvest , 1962 an die National Security Agency geliefert am Atomic Weapons Research Establishment in Aldermaston , England wurde von Forschern dort und bei AERE Harwell intensiv genutzt , aber erst nach der Entwicklung des S2 Fortran Compilers , der als erster dynamische Arrays hinzufügte und später in den Ferranti Atlas von portiert wurde Atlas-Computerlabor in Chilton.

Der 7030 war viel langsamer als erwartet und konnte seine aggressiven Leistungsziele nicht erreichen. IBM war gezwungen, den Preis von 13,5 Millionen US-Dollar auf nur noch 7,78 Millionen US-Dollar zu senken und den 7030 vom Verkauf an Kunden zurückzuziehen, die über die bereits ausgehandelten Verträge hinausgingen. Das Magazin PC World bezeichnete Stretch als einen der größten Fehler im Projektmanagement in der IT- Geschichte.

Innerhalb von IBM schien es schwer zu akzeptieren, von der kleineren Control Data Corporation in den Schatten gestellt zu werden. Der Projektleiter Stephen W. Dunwell wurde zunächst zum Sündenbock für seine Rolle beim "Scheitern" gemacht, aber als der Erfolg des IBM System/360 offensichtlich wurde, wurde er offiziell entschuldigt und 1966 zum IBM . ernannt Gefährte .

Obwohl Stretch seine eigenen Leistungsziele nicht erreichte, diente es als Grundlage für viele der Designmerkmale des erfolgreichen IBM System/360, das 1964 ausgeliefert wurde.

Entwicklungsgeschichte

Anfang 1955 wollte Dr. Edward Teller vom Radiation Laboratory der University of California ein neues wissenschaftliches Rechensystem für dreidimensionale hydrodynamische Berechnungen. Vorschläge für dieses neue System mit dem Namen Livermore Automatic Reaction Calculator oder LARC wurden von IBM und UNIVAC angefordert . Laut IBM-Chef Cuthbert Hurd würde ein solches System etwa 2,5 Millionen US-Dollar kosten und mit ein bis zwei MIPS laufen . Die Lieferung sollte zwei bis drei Jahre nach Vertragsunterzeichnung erfolgen.

Bei IBM arbeitete ein kleines Team bei Poughkeepsie, darunter John Griffith und Gene Amdahl, an dem Designvorschlag. Kurz nachdem sie fertig waren und den Vorschlag präsentieren wollten, hielt Ralph Palmer sie auf und sagte: "Es ist ein Fehler." Das vorgeschlagene Design wäre entweder mit Punktkontakttransistoren oder Oberflächenbarrierentransistoren gebaut worden , die beide wahrscheinlich bald von dem damals neu erfundenen Diffusionstransistor übertroffen werden würden .

IBM kehrte zu Livermore zurück und erklärte, dass sie vom Vertrag zurücktreten würden, und schlug stattdessen ein dramatisch besseres System vor: "Wir werden diese Maschine nicht für Sie bauen, wir wollen etwas Besseres bauen! Wir wissen nicht genau, was es braucht." aber wir glauben, dass es noch eine Million Dollar und ein weiteres Jahr sein wird, und wir wissen nicht, wie schnell es laufen wird, aber wir würden gerne für zehn Millionen Anweisungen pro Sekunde schießen." Livermore war nicht beeindruckt, und im Mai 1955 gaben sie bekannt, dass UNIVAC den LARC- Vertrag gewonnen hatte, der jetzt Livermore Automatic Research Computer heißt . LARC wurde schließlich im Juni 1960 ausgeliefert.

Aus Angst, dass das Los Alamos National Laboratory auch einen LARC bestellen könnte, unterbreitete IBM im September 1955 einen vorläufigen Vorschlag für einen Hochleistungs-Binärcomputer basierend auf der verbesserten Version des von Livermore abgelehnten Designs, den sie mit Interesse erhielten. Im Januar 1956 wurde Project Stretch offiziell initiiert. Im November 1956 gewann IBM den Zuschlag mit dem aggressiven Leistungsziel einer „Geschwindigkeit von mindestens 100 mal IBM 704 “ (also 4 MIPS). Die Auslieferung war für 1960 geplant.

Während der Entwicklung erwies es sich als notwendig, die Taktraten zu reduzieren, was deutlich machte, dass Stretch seine aggressiven Leistungsziele nicht erreichen konnte, aber die Leistungsschätzungen lagen zwischen dem 60- und 100-fachen der IBM 704. 1960 wurde der Preis von 13,5 Millionen US-Dollar festgelegt die IBM 7030. 1961 zeigten aktuelle Benchmarks , dass die Leistung der IBM 7030 nur etwa das 30-fache der IBM 704 (dh 1,2 MIPS) betrug, was für IBM erhebliche Verlegenheit verursachte. Im Mai 1961 kündigte Tom Watson eine Preissenkung aller in Verhandlung befindlichen 7030er auf 7,78 Millionen US-Dollar und die sofortige Rücknahme des Produkts aus dem weiteren Verkauf an.

Seine Gleitkomma- Additionszeit beträgt 1,38–1,50 Mikrosekunden , die Multiplikationszeit beträgt 2,48–2,70 Mikrosekunden und die Divisionszeit beträgt 9,00–9,90 Mikrosekunden.

Technische Auswirkungen

Obwohl die IBM 7030 nicht als erfolgreich angesehen wurde, brachte sie viele Technologien hervor, die in zukünftigen Maschinen enthalten waren, die sehr erfolgreich waren. Die Transistorlogik des Standard Modular Systems war die Grundlage für die IBM 7090- Reihe wissenschaftlicher Computer, die IBM 7070- und 7080- Geschäftscomputer, die IBM 7040- und IBM 1400- Reihen und den IBM 1620 Small Scientific Computer; die 7030 verwendet etwa 170.000 Transistoren. Die IBM 7302 Modell I Kernspeichereinheiten wurden verwendet , auch in der IBM 7090, IBM 7070 und IBM 7080. Multiprogramming , Speicherschutz, generali Interrupts, die Acht-Bit - Byte für E / A waren alle Konzepte später im integrierten IBM System / 360 Reihe von Computern sowie die meisten späteren Central Processing Units (CPU).

Stephen Dunwell, der Projektmanager, der zum Sündenbock wurde, als Stretch kommerziell scheiterte, wies kurz nach der phänomenal erfolgreichen Einführung von System/360 im Jahr 1964 darauf hin, dass die meisten seiner Kernkonzepte von Stretch entwickelt wurden. Bis 1966 hatte er eine Entschuldigung erhalten und wurde zum IBM Fellow ernannt, eine hohe Ehre, die Ressourcen und Autorität mit sich brachte, die gewünschte Forschung zu betreiben.

Instruction Pipelining , Prefetch und Decoding und Memory Interleaving wurden in späteren Supercomputerdesigns wie den IBM System/360 Modellen 91 , 95 und 195 und der IBM 3090- Serie sowie Computern anderer Hersteller verwendet. Ab 2021 werden diese Techniken immer noch in den fortschrittlichsten Mikroprozessoren verwendet, beginnend mit der Generation der 1990er Jahre, die den Intel Pentium und den Motorola/IBM PowerPC umfasste , sowie in vielen eingebetteten Mikroprozessoren und Mikrocontrollern verschiedener Hersteller.

Hardwareimplementierung

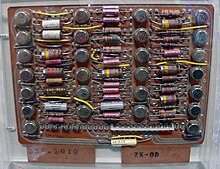

Die 7030 CPU verwendet emittergekoppelte Logik (ursprünglich Stromsteuerungslogik genannt ) auf 18 Typen von Standard Modular System (SMS)-Karten. Es verwendet 4.025 Doppelkarten (wie abgebildet) und 18.747 Einzelkarten, die 169.100 Transistoren enthalten und eine Gesamtleistung von 21 kW benötigen. Es verwendet Hochgeschwindigkeits-NPN- und PNP-Germanium- Drifttransistoren mit einer Grenzfrequenz von über 100 MHz und einem Verbrauch von jeweils ~50 mW. Einige Schaltungen der dritten Ebene verwenden eine dritte Spannungsebene. Jeder Logikpegel hat eine Verzögerung von etwa 20 ns. Um die Geschwindigkeit in kritischen Bereichen zu erhöhen, wird eine Emitterfolgerlogik verwendet, um die Verzögerung auf etwa 10 ns zu reduzieren.

Es verwendet den gleichen Kernspeicher wie die IBM 7090 .

Installationen

- Los Alamos Scientific Laboratory (LASL) im April 1961, angenommen im Mai 1961 und genutzt bis 21. Juni 1971.

- Lawrence Livermore National Laboratory , Livermore, Kalifornien, geliefert im November 1961.

- US National Security Agency im Februar 1962 als Haupt-CPU des IBM 7950 Harvest- Systems, das bis 1976 verwendet wurde, als das IBM 7955 Tractor- Bandsystem Probleme aufgrund abgenutzter Nocken entwickelte, die nicht ersetzt werden konnten.

- Atomic Weapons Establishment , Aldermaston , England, geliefert im Februar 1962

- US Weather Bureau Washington DC, geliefert im Juni/Juli 1962.

- MITRE Corporation , geliefert im Dezember 1962. und bis August 1971 verwendet. Im Frühjahr 1972 wurde es an die Brigham Young University verkauft , wo es bis zur Verschrottung 1982 von der Physikabteilung verwendet wurde.

- US Navy Dahlgren Naval Proving Ground , ausgeliefert Sep/Okt 1962.

- Commissariat à l'énergie atomique , Frankreich, geliefert im November 1963.

- IBM.

Die IBM 7030 des Lawrence Livermore Laboratory (mit Ausnahme des Kernspeichers ) und Teile der IBM 7030 der MITRE Corporation/Brigham Young University befinden sich jetzt in der Sammlung des Computer History Museum in Mountain View, Kalifornien .

Die Architektur

Datenformate

- Festkommazahlen sind in der Länge variabel und werden entweder binär (1 bis 64 Bit) oder dezimal (1 bis 16 Stellen) und entweder im Format ohne Vorzeichen oder im Format Vorzeichen/Größe gespeichert . Im Dezimalformat sind Ziffern Bytes variabler Länge (4 bis 8 Bit).

- Gleitkommazahlen haben ein 1-Bit-Exponenten-Flag, einen 10-Bit-Exponenten, ein 1-Bit-Exponenten-Vorzeichen, eine 48-Bit-Größe und ein 4-Bit-Vorzeichen-Byte im Vorzeichen/Größen-Format.

- Alphanumerische Zeichen haben eine variable Länge und können einen beliebigen Zeichencode von 8 Bit oder weniger verwenden.

- Bytes haben eine variable Länge (1 bis 8 Bit).

Anweisungsformat

Anweisungen sind entweder 32-Bit oder 64-Bit.

Register

Die Register überlagern wie gezeigt die ersten 32 Adressen des Speichers.

| ! Die Anschrift | Gedächtnisstütze | Registrieren | Gespeichert in: |

|---|---|---|---|

| 0 | $Z | 64-Bit-Null: liest immer als Null, kann nicht durch Schreibvorgänge geändert werden | Hauptkernspeicher |

| 1 | $IT | Intervalltimer (Bits 0..18): dekrementiert bei 1024 Hz, zyklisch alle 8,5 Minuten, bei Null schaltet er die "Zeitsignalanzeige" im Anzeigeregister ein | Indexkernspeicher |

| $TC | 36-Bit-Zeituhr (Bits 28..63): Zählung von 1024 Hz Ticks, Bits 38..63 inkrementieren einmal pro Sekunde, recycelt alle ~777 Tage. | ||

| 2 | $IA | 18-Bit-Unterbrechungsadresse | Hauptkernspeicher |

| 3 | $UB | 18-Bit-Obergrenzenadresse (Bits 0-17) | Transistorregister |

| $LB | 18-Bit untere Grenzadresse (Bits 32-49) | ||

| 1-Bit-Grenzkontrolle (Bit 57): bestimmt, ob Adressen innerhalb oder außerhalb der Grenzadressen geschützt sind | |||

| 4 | 64-Bit-Wartungsbits: nur für Wartung verwendet | Hauptkernspeicher | |

| 5 | $CA | Kanaladresse (Bits 12..18): readonly, gesetzt von der "Exchange", einem I/O-Prozessor | Transistorregister |

| 6 | $CPUS | andere CPU-Bits (Bits 0..18): Signalisierungsmechanismus für einen Cluster von bis zu 20 CPUs | Transistorregister |

| 7 | $LZC | Anzahl der linken Nullen (Bits 17..23): Anzahl der führenden Null-Bits aus einem Verknüpfungsergebnis oder einer Gleitkommaoperation | Transistorregister |

| $AOC | All-Ones-Zählung (Bits 44..50): Anzahl der Bits, die im Zusammenhangsergebnis oder dezimal Vielfaches oder Dividieren gesetzt sind | ||

| 8 | $L | Linke Hälfte des 128-Bit- Akkumulators | Transistorregister |

| 9 | $R | Rechte Hälfte des 128-Bit-Akkumulators | |

| 10 | $SB | Akkumulator-Vorzeichenbyte (Bit 0..7) | |

| 11 | $IND | Indikatorregister (Bit 0..19) | Transistorregister |

| 12 | $MASKE | 64-Bit-Maskenregister: Bits 0..19 immer 1, Bits 20..47 schreibbar, Bits 48..63 immer 0 | Transistorregister |

| 13 | $RM | 64-Bit-Restregister: nur durch Integer- und Gleitkomma-Divisionsbefehle gesetzt | Hauptkernspeicher |

| 14 | $FT | 64-Bit-Faktorregister: nur durch die Anweisung "load factor" geändert | Hauptkernspeicher |

| fünfzehn | $TR | 64-Bit-Transitregister | Hauptkernspeicher |

| 16 ... 31 |

$X0 ... $X15 |

64-Bit-Indexregister (sechzehn) | Indexkernspeicher |

Die Akkumulator- und Indexregister arbeiten im Vorzeichen- und Betragsformat .

Speicher

Der Hauptspeicher umfasst 16K bis 256K 64-Bit-Binärwörter in Bänken von 16K.

Der Speicher wurde ölbeheizt/gekühlt, um seine Betriebseigenschaften zu stabilisieren.

Software

- STRETCH-Montageprogramm (STRAP)

- MCP (nicht zu verwechseln mit dem Burroughs MCP )

- Programmiersprachen COLASL und IVY

- FORTRAN- Programmiersprache

Siehe auch

- IBM 608 , das erste kommerziell erhältliche Transistor-Computergerät

- ILLIAC II , ein Transistor-Supercomputer der University of Illinois , der mit Stretch konkurrierte.

Anmerkungen

Verweise

Weiterlesen

- Brooks, Friedrich (2010). „Stretching ist eine großartige Übung – es bringt Sie in Form, um zu gewinnen“. IEEE Annals of the History of Computing . 32 : 4–9. doi : 10.1109/MAHC.2010.26 . S2CID 43480009 .

Externe Links

- Oral History Interview mit Gene Amdahl Charles Babbage Institute , University of Minnesota, Minneapolis. Amdahl bespricht seine Rolle beim Design mehrerer Computer für IBM, einschließlich des STRETCH, IBM 701 , 701A und IBM 704 . Er bespricht seine Arbeit mit Nathaniel Rochester und IBMs Management des Designprozesses für Computer.

- IBM Stretch Collections @ Computer History Museum

- 7030 Datenverarbeitungssystem (IBM Archive)

- IBM Stretch (auch bekannt als IBM 7030 Datenverarbeitungssystem)

- Organisationsskizze von IBM Stretch

- BRL-Bericht zum IBM Stretch

- Planung eines Computersystems – Project Stretch , 1962 Buch.

- IBM 7030-Dokumente bei Bitsavers.org (PDF-Dateien)