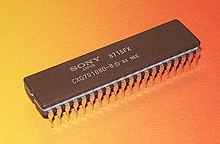

NEC V20 - NEC V20

NEC V20 (µPD70108), 8 MHz

| |

| Allgemeine Information | |

|---|---|

| Gestartet | März 1984 |

| Gängige Hersteller | |

| Leistung | |

| Datenbreite | 16 Bit |

| Physikalische Spezifikationen | |

| Transistoren | |

| Kerne | |

| Co-Prozessor | |

Der NEC V20 war ein Mikroprozessor von NEC . Es war sowohl Pin- als auch Objektcode-kompatibel mit dem Intel 8088 , mit einem Befehlssatz ähnlich dem des Intel 80188 mit einigen Erweiterungen. Der V20 wurde im März 1984 eingeführt.

Merkmale

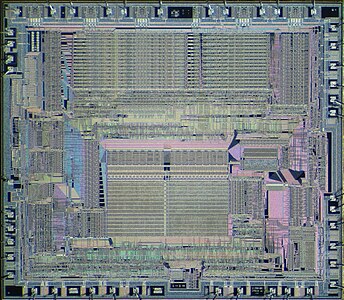

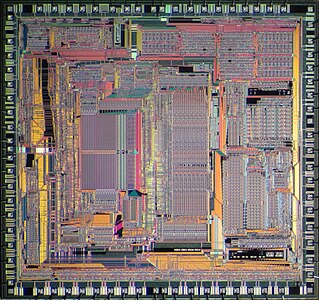

Der Chip des V20 umfasste 63.000 Transistoren , mehr als das Doppelte der 29.000 der 8088-CPU. Der Chip wurde für eine Uhr entworfen Tastverhältnis von 50%, im Vergleich zu dem Zyklus 33% Einschaltdauer von den , dass ein V20 typischerweise gemeint 8088. Internen Differenzen verwendet wurde , könnte weitere Anweisungen in einer bestimmten Zeit als ein Intel 8088 abzuschließen mit der gleichen Frequenz laufen.

Der V20 wurde in 2-Mikron-CMOS-Technologie hergestellt. Frühe Versionen waren verfügbar, die mit Geschwindigkeiten von 5, 8 und 10 MHz liefen . 1990 führte ein Upgrade der Fertigungsverfahrenstechnologie zu den V20H und V20HL mit verbesserter Leistung und reduziertem Stromverbrauch. Spätere Versionen fügten Geschwindigkeiten von 12 und 16 MHz hinzu. Die V20HLs waren auch völlig statisch, sodass ihre Uhr gestoppt werden konnte.

Der V20 wurde intern als 16 Bit breit beschrieben. Es verwendete einen externen 8-Bit-Datenbus, der auf die gleichen Pins wie das Low-Byte des Adressbusses gemultiplext wurde. Sein 20 Bit breiter Adressbus war in der Lage, 1 MB zu adressieren.

Der V20 soll mit dem Intel 8087 Floating Point Unit (FPU) Coprozessor kompatibel gewesen sein. NEC produzierte auch eine eigene FPU, die μPD72091.

Die V30, eine fast identische CPU mit einem 16-Bit breiten externen Datenbus, debütierte am 1. März 1984. Sie war Pin- und Objektcode-kompatibel mit dem Intel 8086.

ISA-Erweiterungen

Die V20- Befehlssatzarchitektur (ISA) umfasste mehrere Befehle, die vom 8088 nicht ausgeführt wurden. Diese umfassten Befehle für die Bitmanipulation, gepackte BCD-Operationen, Multiplikation und Division. Sie enthielten auch neue Real-Mode-Anweisungen vom Intel 80286.

Die Anweisungen ADD4S, SUB4S, und CMP4Swaren in der Lage, riesige gepackte binär codierte Dezimalzahlen , die im Speicher gespeichert sind, zu addieren, zu subtrahieren und zu vergleichen . Anweisungen ROL4und ROR4drehen Sie Vier-Bit- Nibbles . Eine andere Familie bestand aus den Befehlen TEST1, SET1, CLR1, und NOT1, die einzelne Bits ihrer Operanden testen, setzen, löschen und invertieren, aber weit weniger effizient sind als die späteren 180386- Äquivalente BT, BTS, BTR, und BTC; auch sind ihre Kodierungen nicht kompatibel. Es gab zwei Befehle zum Extrahieren und Einfügen von Bitfeldern beliebiger Länge ( EXT, INS). Und schließlich gab es zwei zusätzliche Wiederholungspräfixe REPCund REPNC, die das Original REPEund REPNEAnweisungen zum Scannen einer Reihe von Bytes oder Wörtern (mit Anweisungen SCASund CMPS) ergänzten, während eine weniger oder nicht weniger Bedingung wahr blieb.

Der V20 bot einen Modus, der eine Intel 8080 CPU emulierte . Eine BRKEMAnweisung wird ausgegeben, um die 8080-Emulation zu starten. Der Operand des Befehls gibt eine Interruptnummer an, deren Vektor das Segment:Offset enthält, wo die Emulation beginnen soll. Zum Abschluss wird eine RETEMAnweisung im 8080-Code ausgegeben. Ein nicht häufig verwendetes Merkmal ist CALLN(call native), das einen Interrupt-Aufruf vom Typ 8086 ausgibt, der es ermöglicht, x86-Code (der mit einem zurückgegeben wird IRET) mit 8080-Code zu mischen.

Ein anderer Modus versetzt den Prozessor über eine HALTAnweisung in einen Stromsparzustand .

Klage

1982 verklagte Intel NEC wegen dessen μPD8086 und μPD8088. Diese Klage wurde außergerichtlich beigelegt, wobei NEC zustimmte, die Designs von Intel zu lizenzieren.

Ende 1984 reichte Intel erneut Klage gegen NEC ein und behauptete, dass der Mikrocode im V20 und V30 seine Patente für die 8088- und 8086-Prozessoren verletzte. Der NEC-Softwareingenieur Hiroaki Kaneko hatte sowohl das Hardwaredesign der Intel-CPUs als auch den ursprünglichen Intel-Mikrocode studiert.

In seinem Urteil stellte das Gericht fest, dass der Mikrocode im Kontrollspeicher ein Computerprogramm darstellt und somit urheberrechtlich geschützt ist. Sie stellten außerdem fest, dass Intel sein Urheberrecht verwirkt hatte, indem es versäumte, sicherzustellen, dass alle Second-Source-Chips entsprechend gekennzeichnet waren. Das Gericht stellte außerdem fest, dass NEC nicht einfach den Mikrocode von Intel kopierte und dass sich der Mikrocode im V20 und V30 ausreichend von dem von Intel unterschied, um Intels Patente nicht zu verletzen.

Dieses Urteil begründete die Rechtmäßigkeit des Reverse Engineering.

Varianten und Nachfolger

| Produkt: | Teilenummer: | Einzelheiten: |

|---|---|---|

| NEC V30 | μPD70116 | Im Wesentlichen ein NEC V20 mit einem externen 16-Bit-Datenbus, war der V30 Pin-kompatibel mit dem Intel 8086 . Der V30 war ein werkseitiges Upgrade des 8086, der in der GTD-5 EAX Class 5 Vermittlungsstelle verwendet wurde. Es wurde auch in der Psion Series 3 , dem NEC PC-9801 VM, dem Olivetti PCS86, dem Olivetti PC1, der Applied Engineering "PC Transporter"-Karte für die Apple II- Computerserie und in verschiedenen Arcade-Automaten (insbesondere solchen von von Irem ) in den späten 1980er Jahren. Jahre später wurde eine Niederspannungsversion in Bandais Handheld WonderSwan -Spielekonsole verwendet. |

| NEC V20HL | μPD70108H | High-Speed (bis 16 MHz), Low-Power-Version des V20. |

| NEC V30HL | μPD70116H | High-Speed (bis 16 MHz), Low-Power-Version des V30. |

| NEC V25 | µPD70320 | Eine Mikrocontroller- Version des NEC V20. |

| NEC V25HS | μPD79011 | Eine Version des V25 mit dem RX116 RTOS im internen ROM. |

| NEC V25+ | μPD70325 | Highspeed-Version des V25. |

| NEC V33 | Eine Version des V30 mit getrennten Adress- und Datenbussen und deren Befehlsdecodierung durch eine festverdrahtete Logik und nicht durch einen mikroprogrammierten Steuerspeicher erfolgt. Der Durchsatz ist bei gleicher Taktfrequenz doppelt so hoch wie bei einem V30. Der V33 hat eine Leistung, die der von Intel 80286 entspricht . Der Speicheradressraum wird auf 16 MByte erhöht. Zwei zusätzliche Befehle BRKXAund RETXAunterstützen den erweiterten Adressierungsmodus. Die 8080-Emulation wird nicht unterstützt.

|

|

| NEC V33A | μPD70136A | Unterscheidet sich vom V33 darin, dass es Interrupt-Vektornummern hat, die mit Intels 80X86-Prozessoren kompatibel sind. |

| NEC V35 | μPD70330 | Eine Mikrocontroller-Version des NEC V30. |

| NEC V35HS | μPD79021 | Eine Version des V35 mit dem RX116 RTOS im internen ROM. |

| NEC V35+ | μPD70335 | Eine Hochgeschwindigkeitsversion des V35. |

| NEC V40 | μPD70208 | Eine eingebettete Version des V20, integrierter Intel-kompatibler 8251 USART , 8253 programmierbarer Intervalltimer und 8255 Parallelport-Schnittstelle. Wird in Olivetti PC1, Digisystems Jetta XD und Zenith EZ-PC verwendet. |

| NEC V40HL | μPD70208H | Eine Hochgeschwindigkeits-Niederspannungsversion des V40. |

| NEC V50 | μPD70216 | Eine eingebettete Version des V30. Es ist die Haupt-CPU im Akai S1000 und S1100 sowie im Korg M1 . |

| NEC V50HL | μPD70216H | Eine Hochgeschwindigkeits-Niederspannungsversion des V50. |

| NEC V41 | μPD70270 | Integriert einen V30HL-Kern und PC-XT- Peripheriegeräte: 8255 Parallelport-Schnittstelle, 8254 programmierbarer Intervall-Timer, 8259 PIC, 8237 DMA-Controller und 8042 Tastatur-Controller. Integriert auch einen vollständigen DRAM-Controller. Wurde in Olivetti Quaderno XT-20 verwendet. |

| NEC V51 | μPD70280 | Integriert einen V30HL-Kern und PC-XT- Peripheriegeräte: 8255 Parallelport-Schnittstelle, 8254 programmierbarer Intervall-Timer, 8259 PIC, 8237 DMA-Controller und 8042 Tastatur-Controller. Integriert auch einen vollständigen DRAM-Controller. Wurde in Olivetti Quaderno XT-20 verwendet. |

| NEC V53 | μPD70236 | Integriert einen V33-Kern mit 4-Kanal-DMA (μPD71087/i8237), UART (μPD71051/i8251), drei Timer/Zähler (μPD71054/ i8254 ) und Interrupt-Controller (μPD71059/ i8259 ). Es wurde im Akai MPC3000 und Akai SG01v verwendet . |

| NEC V53A | μPD70236A | Integriert einige Peripheriegeräte mit einem V33A-Kern. |

| NEC V55PI | μPD70433 | |

| Vadem VG230 | Eine Single-Chip-PC-Plattform. Der VG230 enthielt einen 16 MHz NEC V30HL-Prozessor und IBM PC/XT-kompatible Core-Logik, LCD-Controller (CGA/AT&T640x400) mit Touch-Plane-Unterstützung, Tastatur-Matrix-Scanner, Dual- PCMCIA- 2.1-Karten-Controller, EMS 4.0-Hardware-Unterstützung für bis zu 64 MB und integrierte Timer-, PIC-, DMA-, UART- und RTC-Controller. Es wurde in den HP OmniGo 100 , 120 und IBM Simon verwendet . | |

| Vadem VG330 | Als Nachfolger des VG230 enthielt es einen 32 MHz NEC V30MX-Prozessor und IBM PC/AT-kompatible Core-Logik mit zwei PICs, LCD-Controller (640x480), Tastatur-Matrix-Scanner, PC Card ExCA 2.1-Controller und SIR-Port. | |

| NEC V60 | Beginnend mit dem V60-Prozessor verabschiedete sich NEC vom x86-Design. |

- Sterben Fotos

Siehe auch

- NEC RX116 , dediziertes ITRON -1-basiertes 16-Bit-RTOS

- NEC μPD9002 , eine Z80- und x86-kompatible CPU

Verweise

Weiterlesen

- V20/V30-Benutzerhandbuch ; NEC; 228 Seiten; 1986. (Archiv)

- Davis, Randy (Dezember 1985 – Januar 1986). Geschrieben in Greenville, Texas, USA. "Die neuen NEC-Mikroprozessoren - 8080, 8086 oder 8088?" (PDF) . Mikrofüllhorn (27). Bend, Oregon, USA: Micro Cornucopia Inc. S. 4–7. ISSN 0747-587X . Archiviert (PDF) vom Original am 11.02.2020 . Abgerufen am 11.02.2020 .

Externe Links

- Buchty, Rainer. "Casiorama" . www.buchty.net .

- "NEC V20" . cpu-collection.de .

- Hinckley, Robert C. (Januar 1987). "NEC v Intel. Will Hardware in das Schwarze Loch von Copyright - Editors gezogen werden ' " . Santa Clara High-Tech-Rechtszeitschrift . vol. 3 Nr. 1. S. 23–72.