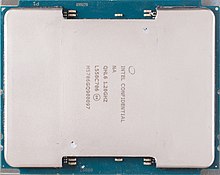

Xeon-Phi - Xeon Phi

| |

| Allgemeine Information | |

|---|---|

| Gestartet | 2010 |

| Abgesetzt | 2020 |

| Leistung | |

| max. CPU- Taktrate | 1,053 GHz bis 1,7 GHz |

| Zwischenspeicher | |

| L1- Cache | 32 KB pro Kern |

| L2-Cache | 512 KB pro Kern |

| Architektur und Klassifizierung | |

| Die Architektur | x86-64 |

| Erweiterungen | |

| Physikalische Spezifikationen | |

| Transistoren | |

| Kerne | |

| Steckdosen) | |

| Produkte, Modelle, Varianten | |

| Markennamen) | |

Xeon Phi ist eine Reihe von x86- Vielkernprozessoren , die von Intel entwickelt und hergestellt wurden . Es ist für den Einsatz in Supercomputern, Servern und High-End-Workstations vorgesehen. Seine Architektur ermöglicht die Verwendung von Standardprogrammiersprachen und Anwendungsprogrammierschnittstellen (APIs) wie OpenMP .

Da es ursprünglich auf einem früheren GPU-Design ( Codename "Larrabee" ) von Intel basierte , das 2009 eingestellt wurde, teilt es sich Anwendungsbereiche mit GPUs. Der Hauptunterschied zwischen Xeon Phi und einer GPGPU wie Nvidia Tesla besteht darin, dass Xeon Phi mit einem x86-kompatiblen Kern mit weniger Modifikationen Software ausführen kann, die ursprünglich auf eine Standard-x86-CPU ausgerichtet war. Es wurde aufgrund mangelnder Nachfrage und Intels Problemen mit seinem 10-nm-Knoten eingestellt.

Zunächst in Form von PCIe- basierten Zusatzkarten wurde im Juni 2013 ein Produkt der zweiten Generation mit dem Codenamen Knights Landing angekündigt. Diese Chips der zweiten Generation könnten als eigenständige CPU und nicht nur als Add-In verwendet werden Karte.

Im Juni 2013 wurde der Supercomputer Tianhe-2 am National Supercomputer Center in Guangzhou (NSCC-GZ) als schnellster Supercomputer der Welt bekannt gegeben (Stand Juni 2018 auf Platz 4). Es verwendete Intel Xeon Phi-Coprozessoren und Ivy Bridge- EP Xeon-Prozessoren, um 33,86 PetaFLOPS zu erreichen.

Die Xeon Phi - Produktlinie direkt mit konkurrierten Nvidia ‚s Tesla und AMD Radeon Instinct Linien tief Lernen und GPGPU - Karten.

Geschichte

| Code Name | Technologie | Kommentare |

|---|---|---|

| Ritterfähre | 45 nm | als PCIe-Karte angeboten; abgeleitet vom Larrabee-Projekt |

| Ritterecke | 22 nm | abgeleitet von P54C; Vektorverarbeitungseinheit; erstes Gerät, das als Xeon Phi . angekündigt wird |

| Ritterlandung | 14 nm | abgeleitet von Silvermont/Airmont (Intel Atom); AVX-512 |

| Ritter Mühle | 14 nm | fast identisch mit Knights Landing, aber für Deep Learning optimiert |

| Ritterhügel | 10 nm | Storniert |

Hintergrund

Die Mikroarchitektur von Larrabee (seit 2006 in Entwicklung) führte sehr breite (512-Bit) SIMD- Einheiten in ein auf x86- Architektur basierendes Prozessordesign ein, erweitert zu einem Cache-kohärenten Multiprozessorsystem, das über einen Ringbus mit dem Speicher verbunden ist; jeder Kern war zu Vier-Wege-Multithreading fähig. Da das Design sowohl für GPUs als auch für Allzweck-Computing gedacht war, enthielten die Larrabee-Chips auch spezielle Hardware für Textur-Sampling. Das Projekt, ein GPU-Produkt für den Einzelhandel direkt aus dem Larrabee-Forschungsprojekt zu produzieren, wurde im Mai 2010 beendet.

Ein weiteres zeitgenössisches Intel-Forschungsprojekt, das eine x86-Architektur auf einem Prozessor mit vielen Multicores implementierte, war der „ Single-Chip Cloud Computer “ (Prototyp eingeführt 2009), ein Design, das ein Cloud-Computing- Rechenzentrum auf einem einzigen Chip mit mehreren unabhängigen Kernen nachahmt : das Prototypdesign beinhaltete 48 Kerne pro Chip mit Hardwareunterstützung für selektive Frequenz- und Spannungssteuerung der Kerne zur Maximierung der Energieeffizienz und integriertes Mesh-Netzwerk für Inter-Chip-Messaging. Dem Design fehlten Cache-kohärente Kerne und es konzentrierte sich auf Prinzipien, die es dem Design ermöglichen würden, auf viele weitere Kerne zu skalieren.

Der Teraflops Research Chip (Prototyp vorgestellt 2007) ist ein experimenteller 80-Kern-Chip mit zwei Gleitkommaeinheiten pro Kern, der eine 96-Bit- VLIW- Architektur anstelle der x86-Architektur implementiert . Das Projekt untersuchte Intercore-Kommunikationsmethoden, das Power-Management pro Chip und erreichte 1,01 TFLOPS bei 3,16 GHz bei einem Stromverbrauch von 62 W.

Ritterfähre

Intels Many Integrated Core (MIC)-Prototyp-Board namens Knights Ferry , das einen Prozessor mit dem Codenamen Aubrey Isle enthält, wurde am 31. Mai 2010 angekündigt. Das Produkt wurde als Derivat des Larrabee- Projekts und anderer Intel-Forschungen einschließlich des Single-Chip-Cloud-Computers bezeichnet .

Das Entwicklungsprodukt wurde als PCIe-Karte mit 32 In-Order-Kernen mit bis zu 1,2 GHz mit vier Threads pro Kern, 2 GB GDDR5-Speicher und 8 MB kohärentem L2-Cache (256 KB pro Kern mit 32 KB L1-Cache) angeboten und ein Leistungsbedarf von ~300 W, gebaut in einem 45-nm-Prozess. Im Kern von Aubrey Isle verbindet ein 1.024-Bit-Ringbus (512-Bit-bidirektional) die Prozessoren mit dem Hauptspeicher. Die Einzelplatinenleistung hat 750 GFLOPS überschritten. Die Prototypplatinen unterstützen nur Gleitkommabefehle mit einfacher Genauigkeit .

Zu den ersten Entwicklern gehörten das CERN , das Korea Institute of Science and Technology Information (KISTI) und das Leibniz Supercomputing Center . Zu den Hardwareanbietern für Prototypenplatinen gehörten IBM, SGI, HP, Dell und andere.

Ritterecke

Die Knights Corner- Produktlinie wird in einer Prozessgröße von 22 nm unter Verwendung von Intels Tri-Gate- Technologie mit mehr als 50 Kernen pro Chip hergestellt und ist Intels erstes kommerzielles Produkt mit vielen Kernen.

Im Juni 2011 gab SGI eine Partnerschaft mit Intel bekannt, um die MIC-Architektur in seinen Hochleistungs-Computing-Produkten zu verwenden. Im September 2011 wurde bekannt gegeben, dass das Texas Advanced Computing Center (TACC) Knights Corner-Karten in seinem 10-petaFLOPS "Stampede"-Supercomputer verwenden wird, der 8 PetaFLOPS Rechenleistung zur Verfügung stellt. Laut "Stampede: A Comprehensive Petascale Computing Environment" werden die "Intel (Knights Landing) MICs der zweiten Generation hinzugefügt, sobald sie verfügbar sind, wodurch die aggregierte Spitzenleistung von Stampede auf mindestens 15 PetaFLOPS erhöht wird".

Am 15. November 2011 zeigte Intel eine frühe Siliziumversion eines Knights Corner-Prozessors.

Am 5. Juni 2012 hat Intel Open-Source-Software und Dokumentation zu Knights Corner veröffentlicht.

Am 18. Juni 2012 gab Intel auf der Hamburg International Supercomputing Conference 2012 bekannt, dass Xeon Phi der Markenname für alle Produkte sein wird, die auf der Many Integrated Core Architektur basieren. Im Juni 2012 kündigte Cray an, 22-nm-"Knight's Corner"-Chips (gekennzeichnet als "Xeon Phi") als Co-Prozessor in seinen "Cascade"-Systemen anzubieten.

Im Juni 2012 kündigte ScaleMP ein Virtualisierungs-Update an, das Xeon Phi als transparente Prozessorerweiterung ermöglicht, sodass Legacy- MMX / SSE- Code ohne Codeänderungen ausgeführt werden kann. Ein wichtiger Bestandteil des Kerns des Intel Xeon Phi Coprozessors ist seine Vector Processing Unit (VPU). Die VPU verfügt über einen neuartigen 512-Bit SIMD-Befehlssatz, der offiziell als Intel Initial Many Core Instructions (Intel IMCI) bekannt ist. Somit kann die VPU 16 Operationen mit einfacher Genauigkeit (SP) oder 8 Operationen mit doppelter Genauigkeit (DP) pro Zyklus ausführen. Die VPU unterstützt auch Fused Multiply-Add (FMA)-Befehle und kann somit 32 SP- oder 16 DP-Gleitkommaoperationen pro Zyklus ausführen. Es bietet auch Unterstützung für Ganzzahlen. Die VPU verfügt außerdem über eine Extended Math Unit (EMU), die Operationen wie Kehrwert, Quadratwurzel und Logarithmus ausführen kann, wodurch diese Operationen vektoriell mit hoher Bandbreite ausgeführt werden können. Die EMU arbeitet, indem sie polynomielle Approximationen dieser Funktionen berechnet.

Am 12. November 2012 kündigte Intel zwei Xeon Phi-Coprozessorfamilien an, die die 22-nm-Prozessgröße verwenden: den Xeon Phi 3100 und den Xeon Phi 5110P. Der Xeon Phi 3100 wird mehr als 1 TeraFLOPS Gleitkommabefehle mit doppelter Genauigkeit mit 240 GB/s Speicherbandbreite bei 300 W verarbeiten können. Der Xeon Phi 5110P wird 1,01 TeraFLOPS Gleitkommabefehle mit doppelter Genauigkeit mit 320 GB/s Speicherbandbreite bei 225 W. Der Xeon Phi 7120P wird 1,2 TeraFLOPS an Gleitkommabefehlen mit doppelter Genauigkeit mit 352 GB/s Speicherbandbreite bei 300 W bewältigen können.

Am 17. Juni 2013 wurde der Supercomputer Tianhe-2 von TOP500 als der schnellste der Welt angekündigt . Tianhe-2 verwendete Intel Ivy Bridge Xeon- und Xeon Phi-Prozessoren, um 33,86 PetaFLOPS zu erreichen. Es war das schnellste auf der Liste seit zweieinhalb Jahren, zuletzt im November 2015.

Design und Programmierung

Die Kerne von Knights Corner basieren auf einer modifizierten Version des P54C- Designs, das im ursprünglichen Pentium verwendet wurde. Die Grundlage der Intel MIC-Architektur besteht darin, x86-Legacy zu nutzen, indem eine x86-kompatible Multiprozessor-Architektur geschaffen wird, die vorhandene Parallelisierungs-Softwaretools verwenden kann. Zu den Programmierwerkzeugen gehören OpenMP , OpenCL , Cilk / Cilk Plus und spezielle Versionen von Intels Fortran-, C++- und Mathematikbibliotheken.

Zu den Designelementen des Larrabee-Projekts gehören x86 ISA, 4-Wege- SMT pro Kern, 512-Bit-SIMD-Einheiten, 32 KB L1-Befehlscache, 32 KB L1-Datencache, kohärenter L2-Cache (512 KB pro Kern) und Ultra-Wide Ringbus, der Prozessoren und Speicher verbindet.

Die 512-Bit-SID-Befehle von Knights Corner teilen viele intrinsische Funktionen mit der AVX-512-Erweiterung. Die Befehlssatzdokumentation ist von Intel unter dem Erweiterungsnamen KNC erhältlich.

- Modelle der Xeon Phi

X100-Serie

| Name | Seriennummer |

Kerne ( Threads @ 4x Kern) |

Takt (MHz) | L2- Cache |

GDDR5 ECC-Speicher | Spitzen-DP- Berechnung (GFLOPS) |

TDP (W) |

Kühlsystem |

Formfaktor | Freigegeben | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Menge | Kanäle |

SW GB/s |

|||||||||

| Xeon Phi 3110X | SE3110X | 61 (244) | 1053 | - | 30,5 MB | 6 GB | 12 | 240 | 1028 | 300 | Blankes Brett | PCIe 2.0 x16-Karte | November 2012 |

| 8 GB | 16 | 320 | |||||||||||

| Xeon Phi 3120A | SC3120A | 57 (228) | 1100 | - | 28,5 MB | 6 GB | 12 | 240 | 1003 | 300 | Lüfter/Kühlkörper | 17. Juni 2013 | |

| Xeon Phi 3120P | SC3120P | 57 (228) | 1100 | - | 28,5 MB | 6 GB | 12 | 240 | 1003 | 300 | Passiver Kühlkörper | 17. Juni 2013 | |

| Xeon Phi 31S1P | BC31S1P | 57 (228) | 1100 | - | 28,5 MB | 8 GB | 16 | 320 | 1003 | 270 | Passiver Kühlkörper | 17. Juni 2013 | |

| Xeon Phi 5110P | SC5110P | 60 (240) | 1053 | - | 30,0 MB | 8 GB | 16 | 320 | 1011 | 225 | Passiver Kühlkörper | 12. November 2012 | |

| Xeon Phi 5120D | SC5120D | 60 (240) | 1053 | - | 30,0 MB | 8 GB | 16 | 352 | 1011 | 245 | Blankes Brett | SFF 230-polige Karte | 17. Juni 2013 |

| BC5120D | |||||||||||||

| Xeon Phi SE10P | SE10P | 61 (244) | 1100 | - | 30,5 MB | 8 GB | 16 | 352 | 1074 | 300 | Passiver Kühlkörper | PCIe 2.0 x16-Karte | 12. Nov. 2012 |

| Xeon Phi SE10X | SE10X | 61 (244) | 1100 | - | 30,5 MB | 8 GB | 16 | 352 | 1074 | 300 | Blankes Brett | 12. Nov. 2012 | |

| Xeon Phi 7110P | SC7110P | 61 (244) | 1100 | 1250 | 30,5 MB | 16 Gigabyte | 16 | 352 | 1220 | 300 | Passiver Kühlkörper | ??? | |

| Xeon Phi 7110X | SC7110X | 61 (244) | 1250 | ??? | 30,5 MB | 16 Gigabyte | 16 | 352 | 1220 | 300 | Blankes Brett | ??? | |

| Xeon Phi 7120A | SC7120A | 61 (244) | 1238 | 1333 | 30,5 MB | 16 Gigabyte | 16 | 352 | 1208 | 300 | Lüfter/Kühlkörper | 6. April 2014 | |

| Xeon Phi 7120D | SC7120D | 61 (244) | 1238 | 1333 | 30,5 MB | 16 Gigabyte | 16 | 352 | 1208 | 270 | Blankes Brett | SFF 230-polige Karte | Marz 2014 |

| Xeon Phi 7120P | SC7120P | 61 (244) | 1238 | 1333 | 30,5 MB | 16 Gigabyte | 16 | 352 | 1208 | 300 | Passiver Kühlkörper | PCIe 2.0 x16-Karte | 17. Juni 2013 |

| Xeon Phi 7120X | SC7120X | 61 (244) | 1238 | 1333 | 30,5 MB | 16 Gigabyte | 16 | 352 | 1208 | 300 | Blankes Brett | 17. Juni 2013 | |

Ritterlandung

Codename für das MIC-Architekturprodukt der zweiten Generation von Intel. Intel gab offiziell am 17. Juni 2013 erstmals Details zu seinen Intel Xeon Phi-Produkten der zweiten Generation bekannt. und mit der 14-nm- Prozesstechnologie von Intel hergestellt werden. Knights Landing-Produkte werden integrierten On-Package-Speicher für eine deutlich höhere Speicherbandbreite enthalten.

Knights Landing enthält bis zu 72 Airmont (Atom)-Kerne mit vier Threads pro Kern und verwendet den LGA 3647- Sockel, der bis zu 384 GB „fernen“ DDR4 2133-RAM und 8–16 GB gestapelten „nahen“ 3D- MCDRAM unterstützt , eine Version des Hybrider Speicherwürfel . Jeder Kern verfügt über zwei 512-Bit-Vektoreinheiten und unterstützt AVX-512 SIMD-Befehle, insbesondere die Intel AVX-512 Foundational Instructions (AVX-512F) mit Intel AVX-512 Conflict Detection Instructions (AVX-512CD), Intel AVX-512 Exponential and Reziproke Anweisungen (AVX-512ER) und Intel AVX-512 Prefetch-Anweisungen (AVX-512PF). Die Unterstützung für IMCI wurde zugunsten von AVX-512 entfernt.

Das National Energy Research Scientific Computing Center gab bekannt, dass in Phase 2 seines neuesten Supercomputing-Systems "Cori" Knights Landing Xeon Phi-Coprozessoren verwendet werden.

Am 20. Juni 2016 hat Intel die Intel Xeon Phi Produktfamilie x200 basierend auf der Knights Landing Architektur auf den Markt gebracht und deren Anwendbarkeit nicht nur für traditionelle Simulationsworkloads, sondern auch für maschinelles Lernen betont . Die bei der Markteinführung angekündigte Modellpalette umfasste nur Xeon Phi mit bootfähigem Formfaktor, aber zwei Versionen davon: Standardprozessoren und Prozessoren mit integrierter Intel Omni-Path- Architektur-Fabric. Letzteres wird durch das Suffix F in der Modellnummer gekennzeichnet. Es wird erwartet, dass integrierte Fabric eine bessere Latenz zu geringeren Kosten bietet als diskrete Hochleistungs-Netzwerkkarten.

Am 14. November 2016 enthielt die 48. Liste der TOP500 10 Systeme mit Knights Landing-Plattformen.

Die PCIe- basierte Co-Prozessor-Variante von Knight's Landing wurde nie dem allgemeinen Markt angeboten und wurde im August 2017 eingestellt. Dazu gehörten die 7220A-, 7240P- und 7220P-Coprozessor-Karten.

Intel hat angekündigt, Knights Landing im Sommer 2018 einzustellen.

- Modelle

Alle Modelle können ihre Spitzengeschwindigkeiten steigern, indem sie ihre Basisfrequenz um 200 MHz erhöhen, wenn sie nur einen oder zwei Kerne betreiben. Bei drei bis zur maximalen Kernzahl können die Chips nur 100 MHz über die Grundfrequenz hinaus steigern. Alle Chips führen High-AVX-Code mit einer um 200 MHz reduzierten Frequenz aus.

| Xeon Phi 7200-Serie |

sSpec- Nummer |

Kerne (Gewinde) |

Takt (MHz) | L2- Cache |

MCDRAM-Speicher | DDR4-Speicher | Spitzen-DP- Berechnung |

TDP (W) |

Steckdose | Veröffentlichungsdatum | Artikelnummer | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Menge | BW | Kapazität | BW | |||||||||

| Xeon Phi 7210 | SR2ME (B0) | 64 (256) | 1300 | 1500 | 32 MB | 16 Gigabyte | 400+ GB/s | 384 GB | 102,4 GB/s | 2662 GFLOPS |

215 | SVLCLGA3647 | 20. Juni 2016 | HJ8066702859300 |

| SR2X4 (B0) | ||||||||||||||

| Xeon Phi 7210F | SR2X5 (B0) | 230 | HJ8066702975000 | |||||||||||

| Xeon Phi 7230 | SR2MF (B0) | 215 | HJ8066702859400 | |||||||||||

| SR2X3 (B0) | ||||||||||||||

| Xeon Phi 7230F | SR2X2 (B0) | 230 | HJ8066702269002 | |||||||||||

| Xeon Phi 7250 | SR2MD (B0) | 68 (272) | 1400 | 1600 | 34 MB | 3046 GFLOPS |

215 | HJ8066702859200 | ||||||

| SR2X1 (B0) | ||||||||||||||

| Xeon Phi 7250F | SR2X0 (B0) | 230 | HJ8066702268900 | |||||||||||

| Xeon Phi 7290 | SR2WY (B0) | 72 (288) | 1500 | 1700 | 36 MB | 3456 GFLOPS |

245 | HJ8066702974700 | ||||||

| Xeon Phi 7290F | SR2WZ (B0) | 260 | HJ8066702975200 | |||||||||||

Ritterhügel

Knights Hill war der Codename für die MIC-Architektur der dritten Generation, für die Intel auf dem SC14 erste Details bekannt gab. Es sollte in einem 10 nm-Prozess hergestellt werden.

Knights Hill sollte im Aurora - Supercomputer des US - Energieministeriums eingesetzt werden , der im Argonne National Laboratory eingesetzt werden sollte . Aurora wurde jedoch verzögert, um eine "fortgeschrittene Architektur" mit Schwerpunkt auf maschinellem Lernen zu verwenden.

Im Jahr 2017 gab Intel bekannt, dass Knights Hill zugunsten einer anderen Architektur abgesagt wurde, die von Grund auf neu entwickelt wurde, um in Zukunft Exascale-Computing zu ermöglichen . Diese neue Architektur wird nun für 2020–2021 erwartet.

Ritter Mühle

Knights Mill ist Intels Codename für ein auf Deep Learning spezialisiertes Xeon Phi-Produkt , das erstmals im Dezember 2017 veröffentlicht wurde. Knights Mill ist in den Spezifikationen fast identisch mit Knights Landing und enthält Optimierungen für eine bessere Nutzung der AVX-512-Anweisungen und ermöglicht Vierwege- Hyper-Threading . Die Gleitkommaleistung mit einfacher und variabler Genauigkeit wurde auf Kosten der Gleitkommaleistung mit doppelter Genauigkeit erhöht.

- Modelle

| Xeon Phi 72x5-Serie |

sSpec-Nummer | Kerne (Gewinde) |

Takt (MHz) | L2- Cache |

MCDRAM-Speicher | DDR4-Speicher | Spitzen-DP- Berechnung |

TDP (W) |

Steckdose | Veröffentlichungsdatum | Artikelnummer | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Menge | BW | Kapazität | BW | |||||||||

| Xeon Phi 7235 | SR3VF (A0) | 64 (256) | 1300 | 1400 | 32 MB | 16 Gigabyte | 400+ GB/s | 384 GB | 102,4 GB/s | TBA | 250 | SVLCLGA3647 | Q4 2017 | HJ8068303823900 |

| Xeon Phi 7285 | SR3VE (A0) | 68 (272) | 1300 | 1400 | 34 MB | 115,2 GB/s | TBA | 250 | HJ8068303823800 | |||||

| Xeon Phi 7295 | SR3VD (A0) | 72 (288) | 1500 | 1600 | 36 MB | 115,2 GB/s | TBA | 320 | HJ8068303823700 | |||||

Programmierung

Eine empirische Performance- und Programmierbarkeitsstudie wurde von Forschern durchgeführt, in der die Autoren behaupten, dass das Erreichen einer hohen Leistung mit Xeon Phi immer noch der Hilfe von Programmierern bedarf und dass es noch weit von der Realität entfernt ist, sich nur auf Compiler mit traditionellen Programmiermodellen zu verlassen. Die Forschung in verschiedenen Bereichen wie Life Sciences und Deep Learning hat jedoch gezeigt, dass die Nutzung sowohl der Thread- als auch der SIMD-Parallelität von Xeon Phi signifikante Geschwindigkeitssteigerungen ermöglicht.

Konkurrenten

- Nvidia Tesla , ein direkter Konkurrent auf dem HPC- Markt

- AMD Radeon Pro und AMD Radeon Instinct direkte Konkurrenten auf dem HPC-Markt

Siehe auch

- Texas Advanced Computing Center – Der Supercomputer "Stampede" enthält Xeon Phi-Chips. Stampede ist zu 10 PetaFLOPS fähig.

- AVX-512

- Zelle (Mikroprozessor)

- Intel Tera-Scale

- Massiv parallel

- Xeon

Verweise

Externe Links

- Intel-Seiten: Intel Xeon Phi-Prozessoren