NOR-Gatter - NOR gate

| Eingang | Ausgabe | |

| EIN | B. | A NOR B. |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Das NOR-Gatter ist ein digitales Logikgatter , das logisches NOR implementiert - es verhält sich gemäß der Wahrheitstabelle rechts. Ein HIGH-Ausgang (1) ergibt sich, wenn beide Eingänge des Gatters LOW (0) sind; Wenn einer oder beide Eingänge HIGH (1) sind, ergibt sich ein LOW-Ausgang (0). NOR ist das Ergebnis der Negation des OR- Operators. In gewissem Sinne kann es auch als Umkehrung eines UND-Gatters angesehen werden . NOR ist eine funktional vollständige Operation - NOR-Gatter können kombiniert werden, um jede andere logische Funktion zu erzeugen. Es teilt diese Eigenschaft mit dem NAND-Gatter . Im Gegensatz dazu ist der OR- Operator monoton, da er nur LOW in HIGH ändern kann, nicht aber umgekehrt.

In den meisten, aber nicht allen Schaltungsimplementierungen ist die Negation kostenlos - einschließlich CMOS und TTL . In solchen Logikfamilien ist OR die kompliziertere Operation; Es kann ein NOR gefolgt von einem NOT verwendet werden. Eine bedeutende Ausnahme bilden einige Formen der Domino-Logik- Familie.

Der ursprüngliche Apollo Guidance Computer verwendete 4.100 integrierte Schaltkreise (IC), von denen jeder nur zwei NOR-Gatter mit drei Eingängen enthielt.

Symbole

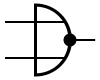

Es gibt drei Symbole für NOR-Gatter: das amerikanische Symbol (ANSI oder "Militär") und das IEC-Symbol ("Europäisch" oder "Rechteck") sowie das veraltete DIN- Symbol. Weitere Informationen finden Sie unter Logikgatter-Symbole . Das ANSI-Symbol für das NOR-Gatter ist ein Standard-ODER-Gatter mit einer angeschlossenen Inversionsblase. Die Blase zeigt an, dass die Funktion des Gates oder invertiert wurde.

|

|

|

| MIL / ANSI-Symbol | IEC-Symbol | DIN-Symbol |

Hardwarebeschreibung und Pinbelegung

NOR-Gatter sind grundlegende Logikgatter und werden als solche in TTL- und CMOS- ICs erkannt . Der Standard-CMOS-IC der Serie 4000 ist der 4001, der vier unabhängige NOR-Gatter mit zwei Eingängen enthält. Das Pinbelegungsdiagramm lautet wie folgt:

Pinbelegung eines 4001 Quad NOR DIP- Formats IC

|

1 Input A1 2 Input B1 3 Output Q1 4 Output Q2 5 Input B2 6 Input A2 7 Vss 8 Input A3 9 Input B3 10 Output Q3 11 Output Q4 12 Input B4 13 Input A4 14 Vdd |

Verfügbarkeit

Diese Geräte sind von den meisten Halbleiterherstellern wie Fairchild Semiconductor , Philips oder Texas Instruments erhältlich . Diese sind normalerweise sowohl im DIP- als auch im SOIC- Format erhältlich. Datenblätter sind in den meisten Datenblattdatenbanken leicht verfügbar .

In den gängigen CMOS- und TTL- Logikfamilien stehen NOR-Gatter mit bis zu 8 Eingängen zur Verfügung:

-

CMOS

- 4001: Quad-NOR-Gatter mit 2 Eingängen

- 4025: Dreifaches NOR-Gatter mit 3 Eingängen

- 4002: Duales NOR-Gatter mit 4 Eingängen

- 4078: Einzelnes NOR-Gatter mit 8 Eingängen

-

TTL

- 7402: Quad-NOR-Gatter mit 2 Eingängen

- 7427: Dreifaches NOR-Gatter mit 3 Eingängen

- 7425: Duales NOR-Gatter mit 4 Eingängen (mit Strobe, veraltet)

- 74260: Duales NOR-Gatter mit 5 Eingängen

- 744078: Einzelnes NOR-Gatter mit 8 Eingängen

In den älteren RTL- und ECL- Familien waren NOR-Gatter effizient und wurden am häufigsten verwendet.

Implementierungen

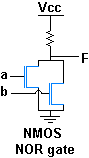

Die obigen Diagramme zeigen den Aufbau eines NOR-Gatters mit 2 Eingängen unter Verwendung einer NMOS-Logikschaltung . Wenn einer der Eingänge hoch ist, wird der entsprechende N-Kanal- MOSFET eingeschaltet und der Ausgang niedrig gezogen; Andernfalls wird der Ausgang durch den Pull-up-Widerstand hochgezogen .

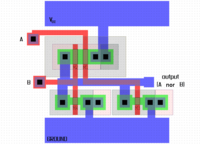

Das folgende Diagramm zeigt ein NOR-Gatter mit 2 Eingängen unter Verwendung der CMOS- Technologie. Die Dioden und Widerstände an den Eingängen sollen die CMOS-Komponenten vor Schäden durch elektrostatische Entladung (ESD) schützen und spielen keine Rolle für die logische Funktion der Schaltung.

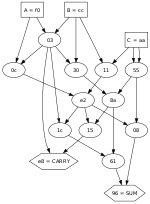

Funktionale Vollständigkeit

Das NOR-Gatter hat die Eigenschaft der funktionalen Vollständigkeit , die es mit dem NAND-Gatter teilt. Das heißt, jede andere Logikfunktion (UND, ODER usw.) kann nur unter Verwendung von NOR-Gattern implementiert werden. Ein ganzer Prozessor kann nur mit NOR-Gattern erstellt werden.

Da NAND-Gatter auch funktional vollständig sind, kann, wenn keine spezifischen NOR-Gatter verfügbar sind, eines unter Verwendung von NAND-Logik aus NAND- Gattern hergestellt werden .

| Gewünschtes Tor | NAND Bau |

|---|---|

|

|

Siehe auch

- UND Tor

- ODER-Gatter

- NICHT Tor

- NAND-Tor

- XOR-Gatter

- XNOR-Tor

- NAND-Logik

- Boolesche Algebra (Logik)

- Flash-Speicher

Verweise