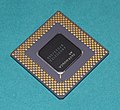

Pin-Grid-Array - Pin grid array

Ein Pin-Grid-Array ( PGA ) ist eine Art integriertes Schaltungsgehäuse . Bei einem PGA ist das Gehäuse quadratisch oder rechteckig, und die Pins sind in einem regelmäßigen Array auf der Unterseite des Gehäuses angeordnet. Die Stifte haben üblicherweise einen Abstand von 2,54 mm (0,1 Zoll) und können die gesamte Unterseite des Gehäuses bedecken oder nicht.

PGAs werden auf oft montiert Leiterplatten unter Verwendung der Durchgangsloch - Verfahren oder eingefügt in eine Steckdose . PGAs ermöglichen mehr Pins pro integriertem Schaltkreis als ältere Gehäuse , wie z. B. Dual-In-Line-Gehäuse (DIP).

PGA-Varianten

Kunststoff

Ein Kunststoff-Pin-Grid-Array-Gehäuse (PPGA) wurde von Intel für neuere Celeron- Prozessoren mit Mendocino-Core auf Basis des Sockels 370 verwendet . Einige Pre-Socket-8-Prozessoren verwendeten ebenfalls einen ähnlichen Formfaktor, obwohl sie nicht offiziell als PPGA bezeichnet wurden.

Flip Chip

Ein Flip-Chip- Pin-Grid-Array (FC-PGA oder FCPGA) ist eine Form eines Pin-Grid-Arrays, bei dem der Chip auf der Oberseite des Substrats nach unten zeigt, wobei die Rückseite des Chips freiliegt. Dies ermöglicht dem Chip einen direkteren Kontakt mit dem Kühlkörper oder einem anderen Kühlmechanismus.

Der FC-PGA wurde von Intel mit den Coppermine-Core- Pentium III- und Celeron- Prozessoren auf Basis von Sockel 370 eingeführt und später für Sockel 478- basierte Pentium-4- und Celeron-Prozessoren verwendet. FC-PGA-Prozessoren passen in Zero Insertion Force (ZIF) Sockel 370- und Sockel 478-basierte Motherboard-Sockel ; ähnliche Pakete wurden auch von AMD verwendet. Es wird noch heute für mobile Intel-Prozessoren verwendet.

Gestaffelter Stift

Das Staggered Pin Grid Array (SPGA) wird von Intel-Prozessoren auf Basis von Sockel 5 und Sockel 7 verwendet . Sockel 8 verwendet ein teilweises SPGA-Layout auf der Hälfte des Prozessors.

Es besteht aus zwei quadratischen Arrays von Pins, die in beide Richtungen um den halben Mindestabstand zwischen den Pins in einem der Arrays versetzt sind. Anders ausgedrückt: Innerhalb einer quadratischen Begrenzung bilden die Pins ein diagonales quadratisches Gitter . Es gibt im Allgemeinen einen Abschnitt in der Mitte des Gehäuses ohne Stifte. SPGA-Packages werden normalerweise von Geräten verwendet, die eine höhere Pindichte erfordern, als ein PGA bieten kann, wie z. B. Mikroprozessoren .

Keramik

Ein Keramik-Pin-Grid-Array (CPGA) ist ein Gehäusetyp, der von integrierten Schaltkreisen verwendet wird . Diese Art der Verpackung verwendet ein Keramiksubstrat mit Pins, die in einem Pin-Grid-Array angeordnet sind. Einige CPUs , die CPGA-Packaging verwenden, sind die AMD- Sockel-A- Athlons und die Duron .

Ein CPGA wurde von AMD für Athlon- und Duron-Prozessoren auf Basis von Sockel A sowie einige AMD-Prozessoren auf Basis von Sockel AM2 und Sockel AM2+ verwendet . Obwohl ähnliche Formfaktoren von anderen Herstellern verwendet wurden, werden sie nicht offiziell als CPGA bezeichnet. Diese Verpackungsart verwendet ein Keramiksubstrat mit in einem Array angeordneten Stiften.

Ein 1,2 GHz VIA C3- Mikroprozessor in einem Keramikgehäuse

Bio

Ein organisches pin grid array (OPGA) ist eine Art von Verbindung für integrierte Schaltungen und insbesondere CPUs , in denen die Silizium Matrize mit einer Platte gebildet aus einem angebrachten wird organischen Kunststoff , die durch eine Anordnung von durchbohrt ist , Stifte , die die erforderlichen Verbindungen herstellen zu die Steckdose .

Die Unterseite eines Celeron -400 in einem PPGA

Zucht

Ein Stud Grid Array (SGA) ist ein Chip-Scale-Package mit kurzen Pins und Pin-Grid-Arrays für den Einsatz in der SMD-Technologie . Der Polymer Stud Grid Array oder Kunststoff Stud Grid Array wurde gemeinsam von dem entwickelten Interuniversity Microelectronics Centre (IMEC) und Labor für Produktionstechnik , Siemens AG .

rPGA

Das reduzierte Pin-Grid-Array wurde von den gesockelten mobilen Varianten der Intel Core i3/5/7-Prozessoren verwendet und weist einen reduzierten Pin-Pitch von 1 mm auf, im Gegensatz zu dem 1,27- mm-Pin-Pitch, der von modernen AMD-Prozessoren und älteren Intel-Prozessoren verwendet wird. Es wird in den Buchsen G1 , G2 und G3 verwendet .

Siehe auch

- Ball-Grid-Array (BGA)

- Zentrierte Quadratzahl

- Chipträger - Chip - Packaging und Pakettypen Liste

- Duales Inline-Paket (DIP)

- Land-Grid-Array (LGA)

- Einzelnes Inline-Paket (SIP)

- Zick-Zack-Inline-Paket (ZIP)

Verweise

Quellen

- Thomas, Andrew (4. August 2010). "Was zum Teufel ist... ein Flip-Chip?" . Das Register . Abgerufen am 30. Dezember 2011 .

- "XSERIES 335 XEON DP-2.4G 512 MB" . CNET. 26. Oktober 2002 . Abgerufen am 30. Dezember 2011 .

- "NOMENKLATUR UND VERPACKUNG DER OBERFLÄCHENMONTAGE" (PDF) .

Externe Links

- Identifizierung des Intel-CPU-Prozessors

- Ball Grid Arrays: the High-Pincount Workhorses , John Baliga, Associate Editor, Semiconductor International , 01.09.1999

- Spot on Komponentenverpackung , 08/1998, Elektronik, Produktion & Prüftechnik

- Terminologie